엔지닉 스터디 2일차이다. 스터디가 반도체 8대공정을 메인 키워드로 하고 있어서 8대공정 위주로만 내용이 구성되어 있을줄 알았는데 어제 한 반도체 기초 이론, 소재 지식, 반도체 공학 내용이나 오늘 다룰 SRAM이나 DRAM, 더 나아가 앞으로 배울 예정으로 써 있는 NAND Flash나 CMP, Cleaning 같은 8대공정은 아니지만 그에 준하는만큼 중요한 공정 등 8대공정 이외의 내용 또한 포함하고 있어 도움이 많이 될 것 같다. 특히나 반도체 취업을 생각하고 있으나, 자신이 지금까지 배운 전공과 하나도 관련이 없다거나 해서 반도체에 관한 지식이 전무한 사람들에게 강력히 추천해도 될만큼 믿음직한 강의가 될 거 같다.

본인은 반도체 8대공정에 관한 어느 정도의 지식을 갖추고 있으나, SRAM, DRAM, NAND Flash와 같은 제품들의 동작 원리에 대해서는 거의 지식이 없다시피한 실정으로, 반도체 8대공정의 기초를 돌아보고 다시 다짐과 동시에 반도체 제품들에 관한 지식도 배울 수 있어 이번 반도체 스터디에 상당히 만족스럽다.

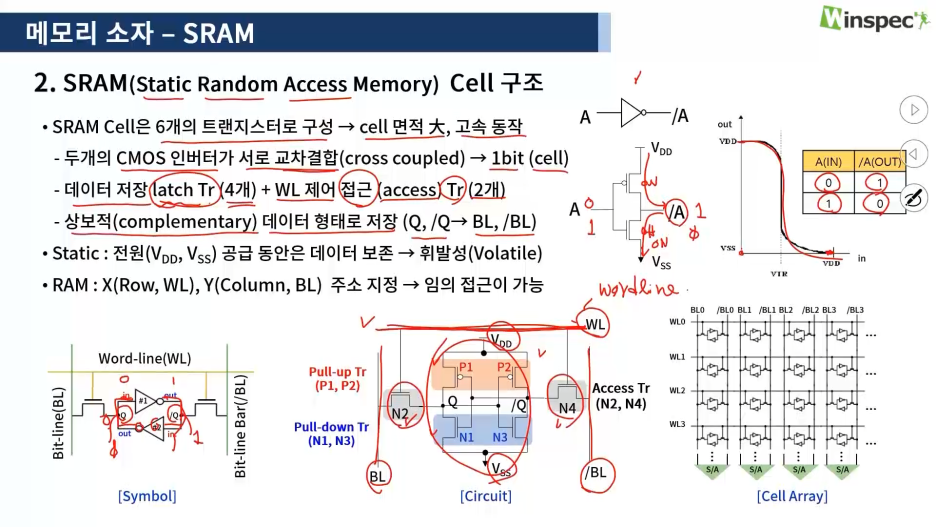

SRAM은 Static Random Access Memory로 컴퓨터에 어느 정도 견문이 있는 사람들이라면 한 번씩은 CPU 스펙에서 Cache Memory라는 단어를 접해 본 경험이 있을 것이다.

그것이 바로 SRAM이다.

여기서 Random Access Memory라 하면

'뭐...? 랜덤 엑세스...? 주사위 돌려서 복불복으로 데이터 불러오는 그런 건가...?' 싶을 텐데 (본인이 그랬다.)

원하는, 임의의 위치의 데이터를 바로 접근할 수 있다는 의미이다.

짜장면을 주문할 때, 주소만 알려주면 바로 번지수 찾아서 배달 음식이 도착하고 그릇을 내놓으면 다시 번지수 찾아서 그릇을 회수하는 그런 시스템과 같다고 할까.

어쨌든 SRAM은 2개의 CMOS Invertors가 서로 교차되어 결합되어 있는 구조로, 여기서 Invertor는 1일 때 0을, 0일 때 1을 출력하는 청개구리같은 녀석이라고 생각하면 된다.

따라서 SRAM의 한 Cell에는 데이터를 저장하는 4개의 Tr.과 WL과 연결된 2개의 Access Tr.로 구성되어 있다.

Capacitor 없이 Tr.로만 구성되어 있기 때문에 DRAM보다 속도가 빠르나 Cell 집적이 어려워 용량이 낮고 가격이 비싸다.

CPU에 내장된 Cache 메모리 용량이 KB, MB 수준밖에 안 되는 한편, DRAM은 4GB부터 시작해서 32GB 64GB까지 나왔으니 말 다했다.

또한 여기서 BL과 WL이 많이 언급될 텐데, BL은 Bit Line의 약어로 데이터의 전달에 관여하는 회로이고

WL은 Word Line의 약어로 Cell 내의 Tr.의 Gate와 연결되어 Cell의 읽기 쓰기 시의 동작을 제어하는 회로이다.

컴퓨터 용량 단위가 비트 바이트인 것을 생각하고 연관시키면 편하다.

나 또한 SRAM에 관한 지식은 많이 낯설고 새로워서 강의에서 배운 것만 살짝 요약하도록 하겠다.

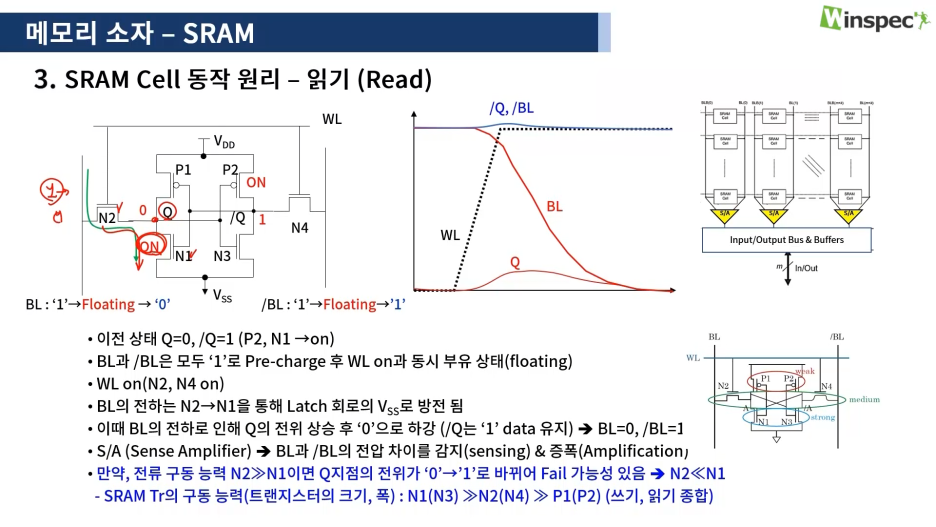

일단 SRAM은 대기 상태일 때, WL이 off 되어 있고 BL, /BL은 1로 pre charge 되어 있다.

그러나 WL이 off 되어 있기에 N2, N4 Tr.의 Channel 영역이 형성되어 있지 않을 테고, 그러니 Cell은 BL과 연결되지 않은 채 Cell 안에서 전류가 서로 순환하며 보존된다.

참고로 이러한 특징 때문에, Capacitor를 이용하여 데이터를 저장하는 DRAM에서는 시간이 흐르면서 누설전류로 Capacitor의 전하가 손실되기 때문에, 주기적으로 데이터를 Refresh시키는 과정이 필요한 반면, SRAM은 그런 과정이 필요하지 않다. (SRAM의 S가 Static인 이유이다.)

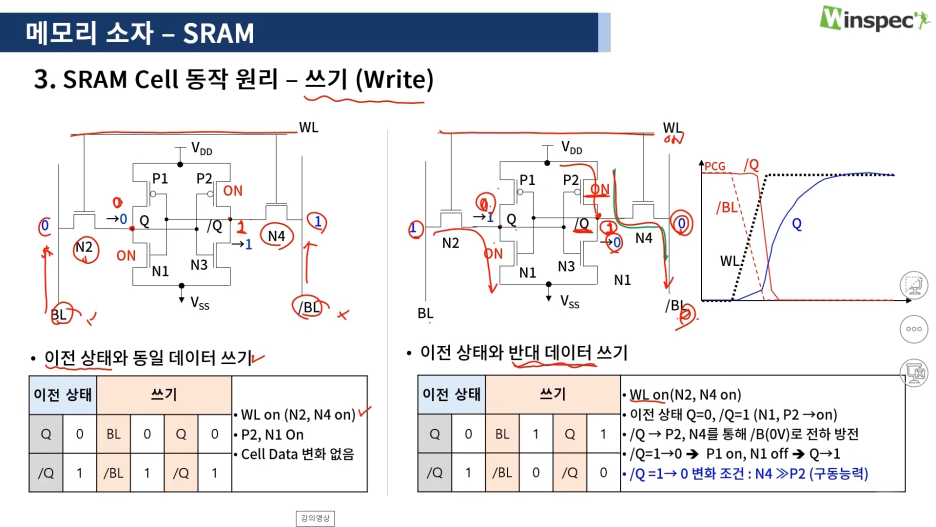

쓰기 상태일 때는, 쓰려는 데이터가 보존되어 있는 데이터와 같을 때와 다를 때, 두 가지의 경우로 나뉜다.

일단 편리하게도 쓰려는 데이터와 동일할 때에는, WL이 On 되어서 N2, N4로 전류가 흘러도 변화가 발생하지 않는다. 그게 끝이다.

기껏 가만히 냅둬도 혼자 잘 간직하고 보존하고 있는데 건드릴 필요가 있겠나.

쓰려는 데이터와 동일하지 않은 데이터를 Cell이 간직하고 있을 때에는 얘기가 조금 달라진다.

Q는 0을, Q/은 1을 간직하고 있고 각각 그곳과 연결된 Bit Line인 BL은 1을, /BL은 0을 띄고 있어, Cell의 데이터와 다른 데이터를 쓰려는 상황을 생각하자.

일단 WL이 On이 되어 N2, N4를 통해 전류가 흐를 수 있게 된다. 즉, 서로 다른 전하량을 가지는 Q와 BL, /Q와 /BL이 서로 만난 셈이다.

그렇다면, /Q에 저장되어 있는 전하가 N4를 통해 전하가 거의 없는 /BL 쪽으로 마구 방전되어 빠져나갈 것이다.

그 결과, /Q는 1에서 0으로 전환되고 -> /Q와 연결되어 있는 NMOS Tr. N1의 흐름이 막히고 PMOS Tr. P1의 흐름이 가능하게 된다.

N1으로 전류 흐름이 막힌 상황에서 BL의 전하는 0을 띄고 있던 Q 쪽으로 밀고 들어왔다가 갈 곳 없이 그대로 그곳에 축적될 것이다.

그 결과, Q는 0에서 1로 전환된다.

그게 끝이다. BL과 Q, /BL과 /Q의 데이터가 같아졌다.

다음은 읽기 과정이다. 일단 쓰기 과정에서 BL, /BL은 pre charge 되어 있지 않다.

전하가 계속 공급되어 흐르는 상황이 아니기 때문에, BL과 /BL은 앞으로의 동작에 의해 1이 될 수도, 0이 될 수도 있다. (Floating)

Cell 내부의 데이터를 BL에 옮겨야 하기 때문에, 역시나 WL이 On 되고 N2, N4을 통해 전류가 흐를 수 있게 된다.

이때, BL의 전하는 0을 띄고 있는 Q 쪽으로 이동하여 들어올 텐데, /Q가 1을 띄어 N1 Tr.이 켜져 있는 탓에 그렇게 BL에서 Q 쪽으로 들어 온 전하는 Vss로 빠져나가 버린다.

즉 계속해서 BL은 Q 쪽으로 밑 빠진 독에 물 붓기를 하고 있는 상황이다. 그러니 BL의 물이 고갈되면 BL은 곧바로 0을 띄게 된다.

/BL 쪽을 한 번 살펴보면 Q가 0인 탓에 N3가 꺼져있고, 따라서 N3를 통해서 전하가 방전되지 않는다. 즉, /BL 쪽의 항아리는 밑이 빠지지 않았다.

그러니 /BL 쪽의 전하는 그대로 가만히 있겠고 그렇게 1을 띄게 된다.

이것이 읽기 과정의 끝이다. Q와 /Q의 데이터가 BL과 /BL에 그대로 옮겨졌다.

뭐 더 하고 싶은 얘기는 많긴 한데, 나조차도 무언가를 설명하고 이게 맞다 틀리다 할 수준은 아니라서,

아쉬운대로 나중에 만반의 준비가 모두 갖춰줬다 싶은 진짜 자신감이 솟구칠 때 심도 있게 글을 써보도록 하겠다.

다음은 DRAM이다.

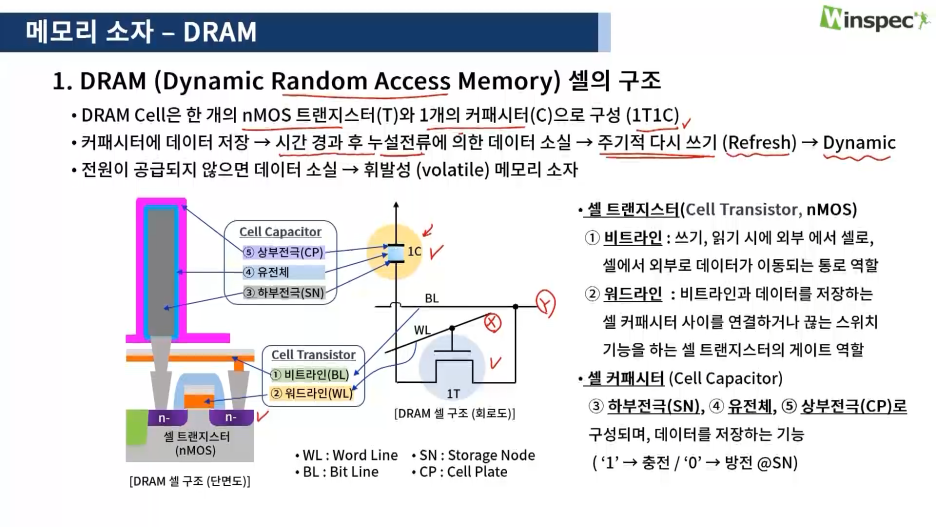

DRAM은 1T1C 구조로 하나의 Cell에 1개의 Tr.과 1개의 Capacitor가 존재하고 있다는 뜻이다.

간단하게 DRAM의 동작을 설명하자면,

Capacitor라는 물탱크가 있고 하부에 달린 Tr.이라는 수도꼭지가 있어서 물탱크 안에 보관된 물의 수위를 조절하면서 그 수위 수준으로 데이터 저장 여부를 결정하는 것이다.

(이렇게 간단했으면 좋겠다.)

여튼 그런 물탱크 비유가 매우 효과적인 탓에, DRAM의 동작은 주로 물탱크 두 개가 연결된 모습으로 비유가 잘 된다.

분명, 1T1C 구조라고 했는데, 물탱크가 왜이리 많지? 싶을 텐데,

1T1C의 데이터 저장 여부에 관여하는 진정한 Capacitor는 수조 모형의 양단에 위치한 길다란 물탱크이고,

각각의 Capacitor와 연결된 큰 수조 둘은 BL이 주변의 BL, WL 혹은 Capacitor의 Plate와 상호작용 하여 생긴 기생 Capacitance를 나타내는 것이다. (Capacitor는 복잡한 게 아니라 그저 두 개의 도체 사이에 유전체가 위치하고 있는 것이 전부임에 유념)

중앙의 S/A은 Sense Amplifier로 BL Capacitor와 /BL Capacitor의 작은 전압차를 감지하여 이를 증폭시키는 역할을 한다.

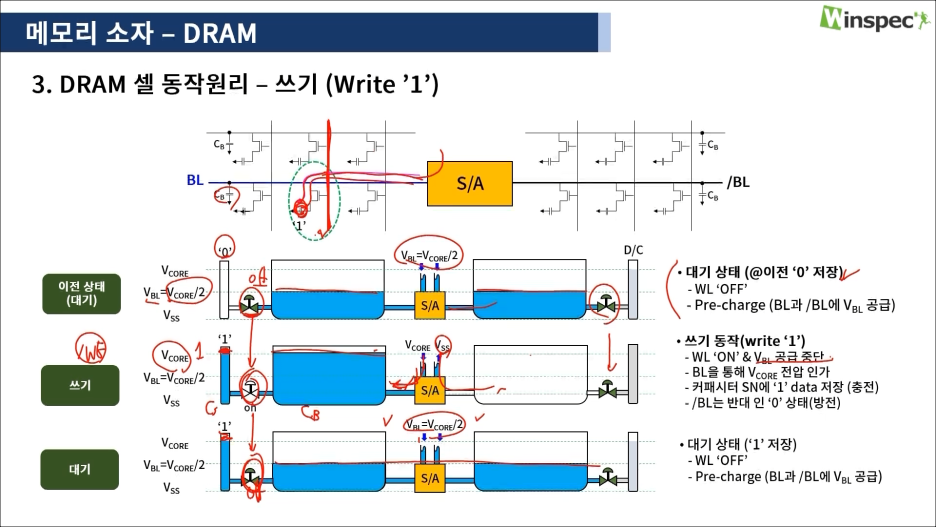

역시 대기 상태일 때, WL은 off 되어 있고 BL과 /BL은 Vcore/2의 값으로 pre charge 되어 있다.

이때, 데이터 값에 따라 Capacitor의 전위는 1인 Vcore일 수도, 0인 Vss일 수도 있다.

Capacitor의 데이터가 0이라고 하고 여기에 1의 값을 쓰는 상황을 가정하자.

여기에서도 WL이 On 되고 BL에는 Vcore를 가하고, /BL은 방전을 유도한다.

WL이 On 되어 Capacitor로의 통로가 연결되어 있는 상황이기 때문에, Vcore를 인가하여 BL에 들어간 전하는 그대로 Capacitor까지 들어가, Capacitor는 Vcore의 전위를 즉 1의 값을 새로 갖게 된다.

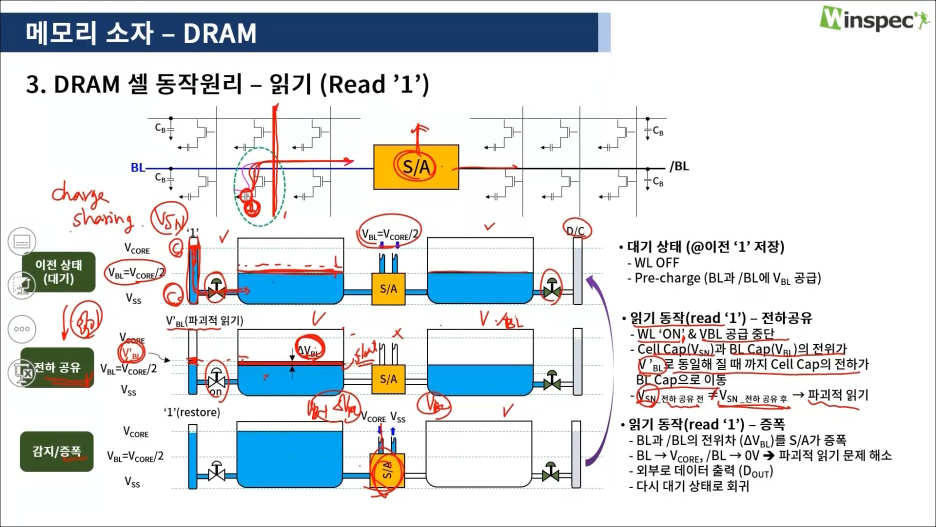

다음은 꽉 찬 Capacitor의 전위를 BL에 복붙해 보겠다. (읽기)

WL이 On 되고, BL과 /BL에는 전압을 가하지 않는다.

그렇다면 Capacitor에 담겨져 있는 전하는 Tr.이 켜져있기 때문에 Tr.을 통해 BL Capacitor로 옮겨올 것이다.

전하는 외부에서 공급되지 않는 상황이기 때문에 고온과 저온의 물체가 접촉 시, 중간의 어느 온도에 서로 도달하여 평형이 이루어지듯이,

Capacitor와 BL Capacitor의 전압이 Vcore/2와 Vcore 사이의 어느 값으로 옮겨갈 것이다.

Capacitor는 읽기 과정 전후로 원본 데이터를 계속 유지하여 1을 띄어야 하나, 이 과정에서 Capacitor의 보유 전하량이 달라지기 때문에, 해당 읽기 과정을 파괴적 읽기라고 부르기도 한다.

물론 이렇게 낮아진 Capacitor의 전위는 다음 단계에서 다시 1로 복구되어 읽기 과정이 끝나도 원본 데이터에는 변화가 없게 된다.

어쨌든 방금의 과정을 전하 공유라고 부른다.

전하 공유가 진행되어, Capacitor의 전위가 높아지고 BL Capacitor의 전위가 높아져 동일한 어느 한 값에 도달하면,

그 새 값을 BL/ Capacitor의 Vcore/2와 비교하여 그 근소한 전압 차이를 감지하고 이를 증폭하는 것이 중앙의 Sense Amplifier의 역할이다.

정말 이름에 충실하다.

다시 BL에는 Vcore가 가해지고 /BL에서는 방전이 일어나면서 (증폭),

Capacitor와 BL Capacitor는 1 수준으로, BL/ Capacitor는 0 수준으로 돌아오게 된다.

이 상황은 아까 본 쓰기 과정에서와 같은 상황으로 쓰기에서와 마찬가지로, BL과 /BL에 다시 Vcore가 가해지면 Cell은 Capacitor가 1의 데이터를 가지는 대기 상태로 복귀하게 된다.

데일리미션

Q1. SRAM의 의미와 특징을 정리해보세요.

SRAM은 Static Random Access Memory의 약자로 6개의 트랜지스터가 하나의 Cell에 들어 있고, 그 구조는 CMOS Invertors 2개가 서로 교차 결합되어 있는 모습이다. Capacitor가 들어있어 시간에 따라 누설전류가 발생하여 주기적으로 데이터를 갱신해야 하는 Refresh 과정이 필요한 DRAM과 다르게 SRAM은 트랜지스터로만 구성되어 Refresh 과정이 불필요하다. 이 때문에 SRAM은 DRAM보다 속도가 빨라 CPU와 같은 연산 장치의 Cache Memory로 주로 사용이 되고 있다. 그러나 SRAM은 DRAM보다 Cell의 집적화가 힘들다는 단점이 존재한다.

Q2. DRAM의 셀 구조에 대해서 설명해보세요.

DRAM은 하나의 트랜지스터가 하나의 Capacitor와 연결되어 있는 1T1C의 구조를 가지는 기억장치이다. DRAM은 Capacitor 내부에 저장된 전하량에 따라 0과 1의 상태를 구분하여 데이터를 저장하기 때문에, 트랜지스터의 Source는 Capacitor와 Drain은 Bit Line과 연결되어 있다. 앞서 말했듯이 DRAM은 누설전류 때문에 Refresh 과정이 불가피한데, 이는 DRAM의 성능을 저하시키는 요인이 되기 때문에 Refresh 과정은 최대한으로 억제될수록 유리하다. 따라서 Capacitor로부터의 전하 손실을 최대한 막아 Refresh 주기를 지연시키고자 Capacitance를 증가시키는 것이 DRAM 성능 발전 방향과 일맥상통한다. DRAM의 Capacitor는 Capacitance를 갖도록 세로로 길게 뻗어있는 구조, 즉 Aspect Ratio가 높은 구조를 갖게 되는데, 이는 DRAM 제조 공정에서의 어려움을 야기한다.