반도체 제품 시리즈 2탄이다. 화학공학과 재학 중이라서, 전공 커리큘럼만을 따라가면 딱히 반도체에 대해 배울 수 있는 기회가 많지 않았다. (4학년 2학기가 다 되어서야 반도체 공정에 대한 과목이 하나있다.) 그래서 어떻게든 학생이라서 다방면으로 배워 볼 수 있을 기회가 있을 때 배워보자라는 마인드로 재료과의 반도체 공학과 반도체 재료, 박막공학을 수강하였는데, 지금 생각해 보면 정말 잘한 결정이라고 생각한다. 그것들로부터 참 많은 것을 배웠다. 그럼에도 재료과라서 그런지 반도체 8대공정과 같이 반도체 제품을 만드는 과정은 많이 다뤘음에도 그렇게 열심히 만들고자 하는 제품의 특징이나 동작 원리 등에 대해서는 심도있게 다루지 못한 점이 있었다. 그래서 많이 아쉬웠고 그런 것들을 배워 보고자 사실 엔지닉 반도체 책을 구매하였던 것이었는데, 이렇게 엔지닉 책하고 연계한 스터디 프로그램에서 DRAM, NAND 등을 배워 볼 수 있어 다행이라고 생각한다.

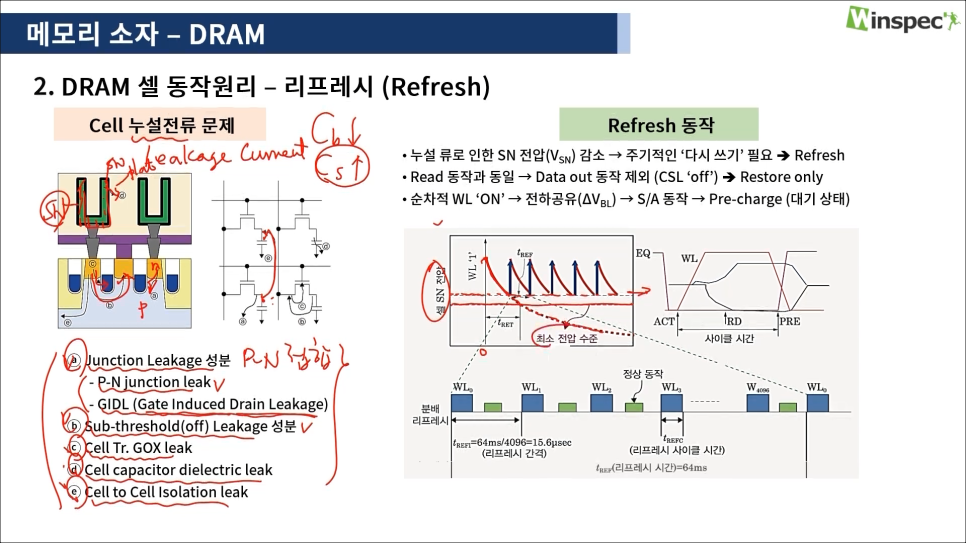

이전에 이어서 DRAM의 Refresh에 대해 배워 보았다.

이전에서 말했듯이, Cell의 Capacitor는 시간에 따라 누설전류가 발생하여 데이터의 손실이 발생할 수밖에 없고,

이를 막기 위하여 주기적으로 데이터를 갱신하는 Refresh 과정이 필요하다고 했다.

Refresh라고 하면 다시 갱신하는 느낌이 들어서 동작 과정이 복잡할 것 같지만, 사실 읽기 과정과 크게 다를 바가 없다.

DRAM의 읽기 과정에서는, pre charge를 끊고 WL을 On 시켜서 Cell Capacitor의 전하를 BL로 이동시켜

두 Capacitor의 전위 수준을 동일하게 맞추는 전하 공유가 일어났고,

그 전하공유로 인하여 근소하게 증가한 전위를 Sense Amplifier가 감지하여 전위가 증가한 BL 쪽에는 Vcore를 가해 다시 1로 만들고

전위가 증가하지 않은 /BL 쪽에는 전압을 가하지 않고 방전시켜 0을 만드는 감지와 증폭 단계가 있었다.

바로 이 후자의 단계, 그러니까 Cell의 Capacitor를 다시 꽉 채우는 것이 Refresh에서 하고자 하는 바와 동일한 것이다.

다만, 읽기는 말 그대로 데이터를 읽고 그것을 복사하여 출력시키는 것인 반면에 Refresh는 데이터를 단순히 다시 갱신하는 것이기 때문에

Refresh 과정에는 읽기 과정과는 다르게 데이터를 출력해 내지는 않는다. (=Column Select Line이 동작하지 않는다.)

Cell Capacitor에서 누설전류가 발생하는 원인에 대해서는 여러가지의 요소가 존재한다.

PN Juncition에서의 누설전류

GIDL에 의한 누설전류

Sub-Threshold 누설전류

Gate Oxide를 통한 누설전류

Capacitor의 Dielectric을 통한 누설전류

Cell 간의 누설전류

이렇게 많은 원인들이 존재하고, 한 가지 확실한 것은 어쨌든 누설전류는 발생하고 Refresh 과정은 불가피하다는 것이다.

그렇다면 또 하나의 문제는 얼마나 자주 Refresh를 하느냐인데, 앞서 말했듯이 Refresh는 동작 속도를 저하시키기 떄문에

마음 같아서는 그냥 하루에 한 번 해버리고 싶겠지만,

아쉽게도 Amplifier가 1의 데이터를 1로 감지하기 위한 Cell Capacitor의 전위의 하한선이 존재한다.

그것을 최소 전압 수준으로 부르며 Capacitor의 Vcore가 누설전류로 최소 전압 수준으로 떨어지기까지의 시간을 Retention Time이라고 부른다.

따라서, Refresh의 주기는 이 Retention Time보다 짧아야 1이 계속 1로 갱신될 수 있다.

다음은 NAND Flash이다.

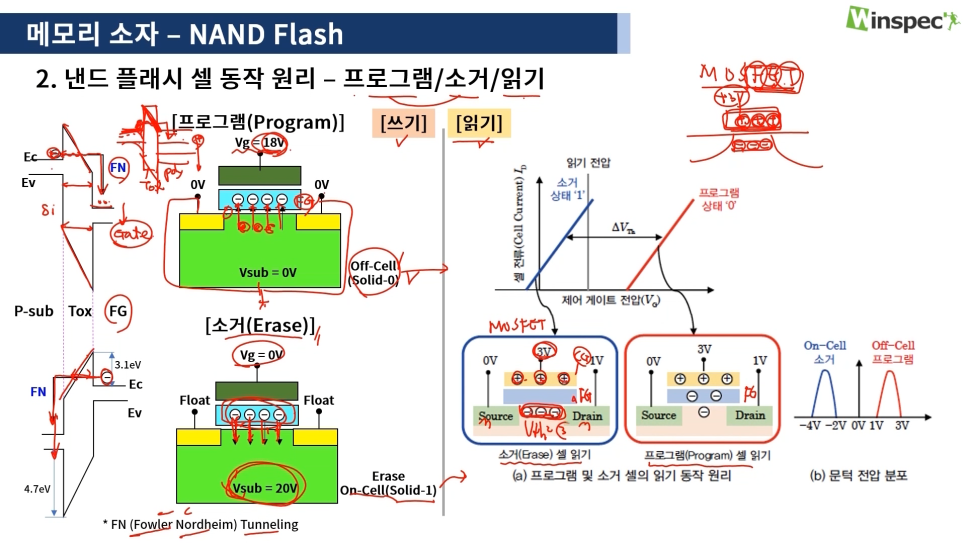

NAND Flash는 Multi Levels의 Gates가 적층되어 있는 구조로, Gate의 종류로는 Control Gate와 Floating Gate가 존재한다.

Control Gate는 WL과 연결된 우리가 예상하는 그런 전형적인 Gate이다만, 특이한 것은 바로 이 Floating Gate이다.

Short Channel Effect에 대해서 좀 살펴 본 사람이라면, 전자의 Tunneling 현상을 들어봤을 것이다.

총탄의 에너지가 크면 관통력이 증가하듯이, 높은 에너지를 받은 전자가 물리적으로 얇은 Oxide를 뚫고 탈출하는 현상이 Tunneling 현상인데, Channel 영역에서 Tunneling 된 전자는 대부분 Oxide 내부에 포집되거나 Gate로 들어갈 수 있어 MOSFET의 전기적 특성을 매우 나쁘게 저하시키는, 피해야 할 현상이다.

그러나 NAND Flash에서는 이 Tunneling 현상을 의도적으로 이용하여 1과 0의 데이터를 저장하는데,

Tunneling 된 전자를 저장하기 위한 곳이 바로 이 Floating Gate이다.

Control Gate에 높은 + 전압이 걸려 많은 수의 전자가 Floating Gate로 Tunneling 하여 들어갔다고 생각해보자.

NMOS 트랜지스터를 켜기 위해서는 게이트에 + 전압을 가해 Channel 영역에 전자의 축적을 유도하고 그로 인해 최종적으로 n형의 Inversion 영역이 생성되어야 한다.

그러나, 본 상황에서는 Channel 영역에 모일 만한 전자의 일부가 Floating Gate 내에 포집되어 있는 상황이기 때문에 Threshold 전압이 그렇지 않을 때보다 증가할 수밖에 없다.

그렇다면 Floating Gate에 전자가 포집된 트랜지스터와 포집되지 않은 트랜지스터에 같은 양의 전압을 Control Gate에 흘려 보냈을 때,

전자가 포집되지 않은 트랜지스터에서는 전류가 흐르는데, 포집된 트랜지스터에서는 전류가 흐르지 않는 전압 구간이 존재하게 될 것이다.

바로 이 구간에서의 트랜지스터의 전류 흐름 여부에 따라 1과 0을 구분하는 것이 NAND의 읽기 쓰기 원리이다.

모든 제조사에서 NAND 용량을 늘리기 위해서 고층 빌딩마냥 다단으로 NAND를 쌓고 있는 사실은 널리 알려져 있다.

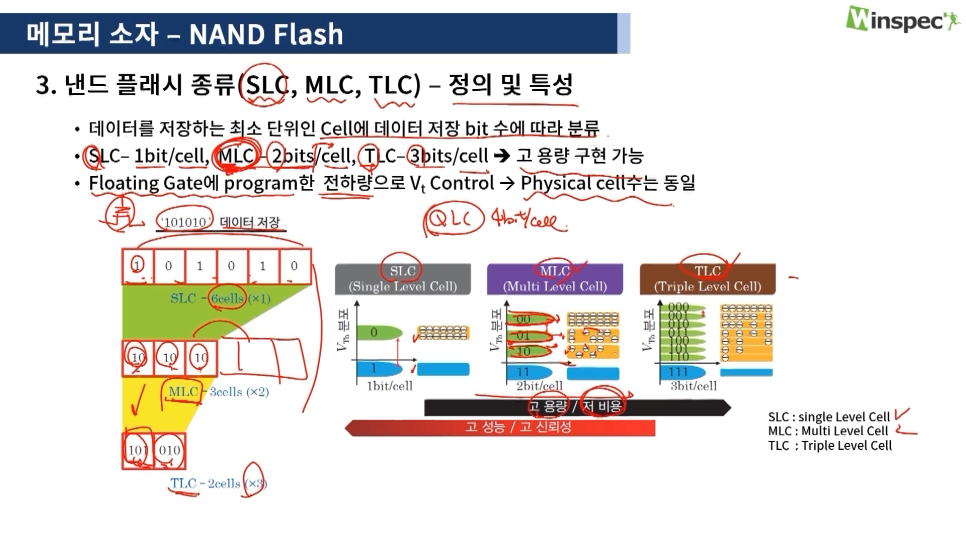

그와 같이 NAND의 용량 효율을 늘리기 위해 개발된 것이 Multi Level Cell (MLC)와 Triple Level Cell (TLC)이다.

이전과 같은 방식에서는 Floating Gate의 전자 포집 여부만으로 단순히 1과 0의 데이터를 구분하였다.

우리는 이것을 Single Level Cell (SLC)라고 부른다.

그러다가 '왜 굳이 전자 있나 없나로만 따지지? 전자 양에 따라서 구분지으면 1, 0 두 개보다 더 많이 구분할 수 있잖아?' 해서 나온 물건이 바로 MLC, TLC이다.

MLC는 2비트 데이터 00, 01, 10, 11 4개를 구분하고 TLC는 3비트 데이터 000, 001, 010, 011, 100, 101, 110, 111 8개를 구분한다.

물론 구분 데이터가 늘어날수록 Floating Gate 내의 전자 양을 세밀하고 조절, 감지해야 되고 읽고 쓰기 회수도 저장 데이터 수에 따라 늘어나기에

단순히 1, 0만 생각했던 SLC의 경우보다 MLC, TLC가 신뢰성, 속도, 수명 등에서 불리하지만...

사실 SLC로는 용량 증대에 명확한 한계가 있기 때문에, 세계의 기업체들은 MLC, TLC 방식에서 성능을 높이는 방법을 파고 있고

(현재 QLC가 개발되고 있다.)

성과가 꽤나 있어서 현재 시중의 MLC, TLC는 수명을 뺀 모든 면에서 SLC의 성능을 뛰어 넘은 상황이며, SLC는 단종된지 오래이다.

데일리미션

Q1. 셀 누설 전류의 원인에 대해 정리해보세요.

Cell 내의 Capacitor에서 누설전류가 발생하게 되어, DRAM에서는 데이터를 갱신하기 위한 Refresh 과정이 불가피하다. 이러한 Capacitor의 전류 누설의 원인에는 PN Junction에서의 누설전류나 Oxide를 통한 누설전류와 같이 결함에 의한 원인이 있고, Gate와 Drain의 Depletion 영역이 겹치는 구간에서 Band Bending에 의해 Valence Band에서 Conduction Band로 Band to Band Tunneling이 일어나는 GIDL과 같은 구조적 요인에 의한 원인이 있는데, 특히 GIDL은 DRAM Capacitor의 누설전류에 큰 영향을 미치는 것으로 밝혀졌다.

Q2. 낸드 플래시 메모리의 종류 이름과 각 특징을 간단히 작성해보세요.

낸드 플래시 메모리는 Cell을 밀도 있게 적층하여 저장 데이터를 늘릴 수 있지만, Cell 내에 저장될 수 있는 데이터 자체를 늘릴 수도 있다. Cell 내에 저장될 수 있는 데이터를 늘리는 것은 Cell 내의 데이터 구분을 조금 더 세밀화하여 이뤄 낼 수 있으며, 그 구분 기준에 따라 낸드 플래시 메모리는 SLC, MLC, TLC로 나뉠 수 있다. 종래의 방법처럼 단순히 Floating Gate 내의 전자 포집 여부를 구분한 것이 SLC, 포집된 전자의 존재 여부가 아닌 양에 따라 구분을 지은 것이 MLC와 TLC이다. SLC, MLC, TLC는 각각 1비트, 2비트, 3비트의 데이터를 저장할 수 있어 낸드 플래시 메모리의 단위 면적당 용량을 크게 향상시킬 수 있지만, 구분 기준을 더 세밀하게 만든만큼 소자 작동에 엄격한 조절이 요구되며 그에 따라 신뢰성 또한 낮아진다는 단점과 함께 읽기 쓰기의 회수가 증가하여 속도 또한 감소한다는 단점이 있다. 그러나 SLC 방식으로는 용량 증대에 있어 MLC, TLC와 같은 방식보다 매우 효율적이지 않기 때문에 현재 낸드 플래시 메모리는 MLC, TLC, 더 나아가 QLC 방식에서 성능을 높이는 방향으로 개발되고 있다.